# 400G OSFP112-RHS(Flat top) DR4 transceiver with 4x 100G PAM4 Optical Interface and 4x 100G PAM4 Electrical interface P/N POOS40DR4-RHS

#### **Features**

- OSFP-RHS Flat Top form factor hot pluggable

- CMIS compliance

- Optical Interface: IEEE 802.3bs compliant

- Electrical Interface: IEEE 802.3ck 400GAUI-4

- optical port of MPO-12/APC

- Up to 500m transmission on SMF with KP4 FEC

- 12 Watts max

- Case temperature range of 0°C to 70°C

#### **Order Info**

| POOS40DR4-<br>RHS  Pro-optics 400G OSFP112-RHS(Flat top) DR4 transceiver, MPO-<br>12 APC interface, 1310nm, up to 500m with SMF, Pull tab, |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|

#### **Descriptions**

This product is an 400Gb/s Octal Small Form-factor Pluggable (OSFP) optical module without integrated heat sink designed for 500m with single mode fiber optical communication applications. The module converts 4 channels of 100Gb/s (PAM4) electrical input data to 4 channels of parallel optical signals. Reversely, on the receiver side, the module converts 4 channels of parallel optical signals of 100Gb/s into 4 channels of 100Gb/s (PAM4) electrical output data.

MPO-12 connector can be plugged into the OSFP112 DR4 module. Proper alignment is ensured by the guide pins inside the receptacle. The cable usually cannot be twisted for proper channel to channel alignment. Electrical connection is achieved through an OSFP MSA-compliant edge type connector.

I2C interface is supported to read and control the status of this product.

12C Management Interface(Micro Controller) CH1 CH1 Tx1 4x Tx Path : MPO12/APC (EML) CH4 CH4 Tx4 Tx4 4x100G PAM4 DSP CH1 CH1 Rx1 : : 4x Rx PD (Array) CH4 Rx4

Figure 1 shows the transceiver block diagram

#### **Transceiver Block Diagram**

#### **Key Features**

The transceiver complies with common management interface specification (CMIS). The supported key features listed below allow host software to read and control the transceiver status through I2C.

- Adaptive Tx input equalization

- Programmable Rx output amplitude

- Programmable Rx output pre-cursor

- Programmable Rx output post-cursor

- Supply voltage monitoring (DDM\_Voltage)

- Transceiver case temperature monitoring (DDM\_Temperature)

- Tx transmit optical power monitoring for each lane (DDM\_TxPower)

- Tx bias current monitoring for each lane (DDM\_TxBias)

- Rx receive optical power monitoring for each lane (DDM\_RxPower)

- Warning and alarm indication for each DDM function

- Tx & Rx LOL and LOS indication

- Tx fault indication

- Host and line side loopback capabilities

- Host and line side PRBS generator and checker capabilities

- CDB firmware upgrade capability

- Versatile diagnostics monitoring (VDM) capability (optional, additional power consumption increase)

- Other functions defined in CMIS

#### **Applications**

The transceiver is designed for Ethernet, Telecom and Infiniband use cases. The application advertisements listed below allow host software to select proper application following CMIS definition

- Application case 1, 1x400G DR4, 1 of 400G per port point to point connections.

- Application case 2, 4x100G DR, 4 of 100G per channel breakout

connections. Table 1 shows CMIS application advertisements list:

Table 1. CMIS Application advertisements

| ApSel<br>Code | Host Electrical<br>Interface | Module Media<br>Interface | Host and Media Lane Count | Host Lane<br>Assignment |

|---------------|------------------------------|---------------------------|---------------------------|-------------------------|

| ApSel 1       | 4F(400GAUI-4-S C2M)          | 1C (400GBASE-DR4)         | 44 (4:4)                  | 01 (lanes 1)            |

| ApSel 2       | 4B(100GAUI-1-S C2M)          | 14(100GBASE-DR)           | 11 (1:1)                  | 0F (lanes 1,2,3,4)      |

| ApSel 3       | 32 ( IB NDR)                 | 1C (400GBASE-DR4)         | 44 (4:4)                  | 01 (lanes 1)            |

## **Pin Map and Description**

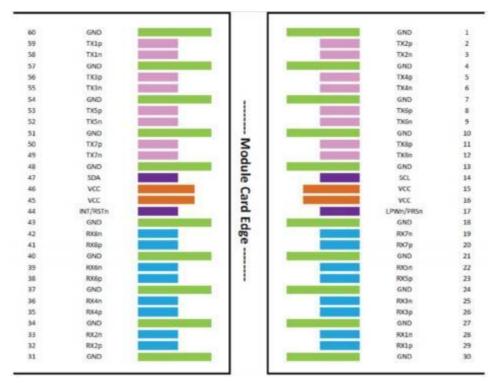

The electrical interface of OSFP module consist of a 60 contacts edge connector as illustrated by the diagram in Figure 2, which defined in Clause 8.1 of OSFP MSA Specification.

Figure 2. MSA Compliant Connector

Table 2 shows the detailed pin list

| Table 2 OSFP connector pin list |               |                                    |                |                 |                  |  |  |

|---------------------------------|---------------|------------------------------------|----------------|-----------------|------------------|--|--|

| Pin#                            | Symbol        | Description                        | Logic          | Direction       | Plug<br>Sequence |  |  |

| 1                               | GND           |                                    | Ground         |                 | 1                |  |  |

| 2                               | TX2p          | Transmitter Data Non-Inverted      | CML-I          | Input from Host | 3                |  |  |

| 3                               | TX2n          | Transmitter Data Inverted          | CML-I          | Input from Host | 3                |  |  |

| 4                               | GND           |                                    | Ground         |                 | 1                |  |  |

| 5                               | TX4p          | Transmitter Data Non-Inverted      | CML-I          | Input from Host | 3                |  |  |

| 6                               | TX4n          | Transmitter Data Inverted          | CML-I          | Input from Host | 3                |  |  |

| 7                               | GND           |                                    | Ground         |                 | 1                |  |  |

| 8                               | TX6p          | Transmitter Data Non-Inverted      | CML-I          | Input from Host | 3                |  |  |

| 9                               | TX6n          | Transmitter Data Inverted          | CML-I          | Input from Host | 3                |  |  |

| 10                              | GND           |                                    | Ground         |                 | 1                |  |  |

| 11                              | TX8p          | Transmitter Data Non-Inverted      | CML-I          | Input from Host | 3                |  |  |

| 12                              | TX8n          | Transmitter Data Inverted          | CML-I          | Input from Host | 3                |  |  |

| 13                              | GND           |                                    | Ground         |                 | 1                |  |  |

| 14                              | SCL           | 2-wire Serial interface clock      | LVCMOS-<br>I/O | Bi-directional  | 3                |  |  |

| 15                              | VCC           | +3.3V Power                        |                | Power from Host | 2                |  |  |

| 16                              | VCC           | +3.3V Power                        |                | Power from Host | 2                |  |  |

| 17                              | LPWn/PRS<br>n | Low-Power Mode / Module<br>Present | Multi-Level    | Bi-directional  | 3                |  |  |

| 18                              | GND           |                                    | Ground         |                 | 1                |  |  |

| 19                              | RX7n          | Receiver Data Inverted             | CML-O          | Output to Host  | 3                |  |  |

| 20                              | RX7p          | Receiver Data Non-Inverted         | CML-O          | Output to Host  | 3                |  |  |

| 21                              | GND           |                                    | Ground         |                 | 1                |  |  |

| 22                              | RX5n          | Receiver Data Inverted             | CML-O          | Output to Host  | 3                |  |  |

| 23                              | RX5p          | Receiver Data Non-Inverted         | CML-O          | Output to Host  | 3                |  |  |

| 24                              | GND           |                                    | Ground         | _               | 1                |  |  |

| 25                              | RX3n          | Receiver Data Inverted             | CML-O          | Output to Host  | 3                |  |  |

| 26                              | RX3p          | Receiver Data Non-Inverted         | CML-O          | Output to Host  | 3                |  |  |

| 27                              | GND           |                                    | Ground         |                 | 1                |  |  |

| 28                              | RX1n          | Receiver Data Inverted             | CML-O          | Output to Host  | 3                |  |  |

| 29                              | RX1p          | Receiver Data Non-Inverted         | CML-O          | Output to Host  | 3                |  |  |

| 30                              | GND           |                                    | Ground         |                 | 1                |  |  |

| 31                              | GND           |                                    | Ground         | 0               | 1                |  |  |

| 32                              | RX2p          | Receiver Data Non-Inverted         | CML-O          | Output to Host  | 3                |  |  |

| 33                              | RX2n          | Receiver Data Inverted             | CML-O          | Output to Host  | 3                |  |  |

| 34                              | GND           |                                    | Ground         |                 | 1                |  |  |

| 35                              | RX4p          | Receiver Data Non-Inverted         | CML-O          | Output to Host  | 3                |  |  |

| 36                              | RX4n          | Receiver Data Inverted             | CML-O          | Output to Host  | 3                |  |  |

| 37                              | GND           | December Del Al                    | Ground         | Outout 4 - 11 4 | 1                |  |  |

| 38                              | RX6p          | Receiver Data Non-Inverted         | CML-O          | Output to Host  | 3                |  |  |

| 39                              | RX6n          | Receiver Data Inverted             | CML-O          | Output to Host  | 3                |  |  |

| 40                              | GND           | Describer Details 1                | Ground         | Output to Uset  | 3                |  |  |

| 41                              | RX8p          | Receiver Data Non-Inverted         | CML-O          | Output to Host  |                  |  |  |

| 42                              | RX8n          | Receiver Data Inverted             | CML-O          | Output to Host  | 3                |  |  |

| 43                              | GND           |                                    | Ground         |                 | 1                |  |  |

## pro-optics

| 44 | INT/RSTn | Module Interrupt / Module Reset | Multi-Level    | Bi-directional  | 3 |

|----|----------|---------------------------------|----------------|-----------------|---|

| 45 | VCC      | +3.3V Power                     |                | Power from Host | 2 |

| 46 | VCC      | +3.3V Power                     |                | Power from Host | 2 |

| 47 | SDA      | 2-wire Serial interface data    | LVCMOS-<br>I/O | Bi-directional  | 3 |

| 48 | GND      |                                 | Ground         |                 | 1 |

| 49 | TX7n     | Transmitter Data Inverted       | CML-I          | Input from Host | 3 |

| 50 | TX7p     | Transmitter Data Non-Inverted   | CML-I          | Input from Host | 3 |

| 51 | GND      |                                 | Ground         |                 | 1 |

| 52 | TX5n     | Transmitter Data Inverted       | CML-I          | Input from Host | 3 |

| 53 | TX5p     | Transmitter Data Non-Inverted   | CML-I          | Input from Host | 3 |

| 54 | GND      |                                 | Ground         |                 | 1 |

| 55 | TX3n     | Transmitter Data Inverted       | CML-I          | Input from Host | 3 |

| 56 | TX3p     | Transmitter Data Non-Inverted   | CML-I          | Input from Host | 3 |

| 57 | GND      |                                 | Ground         |                 | 1 |

| 58 | TX1n     | Transmitter Data Inverted       | CML-I          | Input from Host | 3 |

| 59 | TX1p     | Transmitter Data Non-Inverted   | CML-I          | Input from Host | 3 |

| 60 | GND      |                                 | Ground         |                 | 1 |

|    |          |                                 |                |                 |   |

Table 3 shows the detailed control pins

**Table 3. OSFP Control pins**

| Name      | Direction    | Description                                                                                                                                                                                                                           |

|-----------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCL       | BiDir        | 2-wire serial clock signal. Requires pull-up resistor to 3.3V on host                                                                                                                                                                 |

| SDA       | BiDir        | 2-wire serial data signal. Requires pull-up resistor to 3.3V on host.                                                                                                                                                                 |

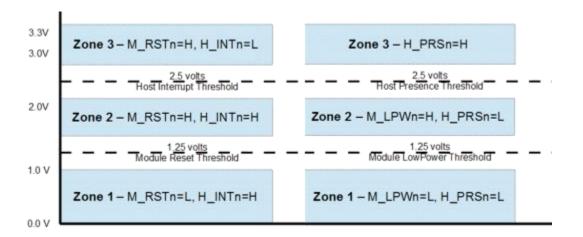

| LPWn/PRSn | Input/Output | Dual Function Signal . Low Power mode is an active-low input signal . Module Present is controlled by a pull-down resistor on the module which gets converted to an active-low output logic signal Voltage zones is shown as figure3. |

| INT/RSTn  | Input/Output | Dual Funtion Signal . Reset is an active-low input signal . Interrupt is an active-high output signal Voltage zones is shown as figure 3.                                                                                             |

#### Figure 3. Voltage Zones

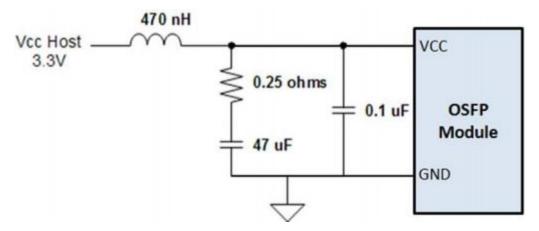

Figure 4 shows the recommended power supply filter design

Figure 4. Recommended Power Supply Filter

#### **Optical Port Description**

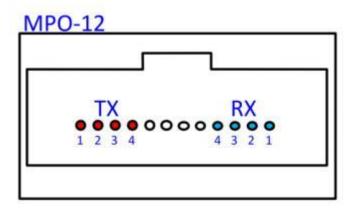

The optical interface port is MPO-12 receptacle. The transmit and receive optical lanes shall occupy the positions depicted in Figure 5 when looking into the MDI receptacle with the connector keyway feature on top.

Figure 5. Optical Media Dependent Interface port assignments

#### **Specification**

#### **Absolute Maximum Ratings**

It has to be noted that the operation in excess of any individual absolute maximum ratings might cause permanent damage to this module.

| Parameter                  | Symbol | Min  | Max | Units | Notes |

|----------------------------|--------|------|-----|-------|-------|

| Storage Temperature        | Ts     | -40  | 85  | degC  |       |

| Operating Case Temperature | Тор    | 0    | 70  | degC  |       |

| Power Supply Voltage       | Vcc    | -0.5 | 3.6 | V     |       |

| Delete all selett (see a see lesselles) | DII | _ | 0.5 | 0.4 |  |

|-----------------------------------------|-----|---|-----|-----|--|

| Relative Humidity (non-condensation)    | KH  | 0 | 85  | %   |  |

### **Recommended Operating Conditions**

| Parameter                  | Symbol          | Min   | Typical | Max                  | Units | Notes |

|----------------------------|-----------------|-------|---------|----------------------|-------|-------|

| Operating Case Temperature | T <sub>OP</sub> | 0     |         | 70                   | degC  |       |

| Power Supply Voltage       | Vcc             | 3.135 | 3.3     | 3.465                | V     |       |

| Data Rate, each Lane       |                 |       | 53.125  |                      | GBd   | PAM4  |

| Data Rate Accuracy         |                 | -100  |         | 100                  | ppm   |       |

| Pre-FEC Bit Error Ratio    |                 |       |         | 2.4x10 <sup>-4</sup> |       |       |

| Post-FEC Bit Error Ratio   |                 |       |         | 1x10 <sup>-12</sup>  |       | 1     |

| Link Distance (SMF)        | D1              | 2     |         | 500                  | m     | 2     |

#### Notes:

- 1. FEC provided by host system.

- 2. FEC required on host system to support maximum distance.

#### **Electrical Characteristics**

The following electrical characteristics are defined over the Recommended Operating Environment unless otherwise specified.

| Parameter                                                                                                  | Test<br>Point | Min                               | Typical      | Max  | Units | Notes |

|------------------------------------------------------------------------------------------------------------|---------------|-----------------------------------|--------------|------|-------|-------|

| Power Consumption                                                                                          |               |                                   |              | 12.0 | W     |       |

| Supply Current                                                                                             | lcc           |                                   |              | 3.83 | Α     |       |

|                                                                                                            | Modu          | le Input (eacl                    | h Lane)      |      |       |       |

| Signaling Rate, each Lane                                                                                  | TP1           | 53.                               | 125 ± 100 pp | om   | GBd   |       |

| Differential pk-pk voltage tolerance                                                                       | TP1a          | 750                               |              |      | mV    |       |

| Peak-to-peak AC common- mode voltage tolerance Low-frequency,VCM <sub>LF</sub> Full-band,VCM <sub>FB</sub> | TP1a          | 32<br>80                          |              |      | mV    |       |

| Differential-mode to common-mode return loss, RLcd                                                         | TP1           | IEEE 802.3c k Equatio n (120G -2) |              |      | dB    |       |

| Effective return loss, ERL                                                                                 | TP1           | 8.5                               |              |      | dB    |       |

| Differential termination mismatch                                                                          | TP1           |                                   |              | 10   | %     |       |

| Module stressed input tolerance Single-ended voltage tolerance range  DC common-mode voltage                | TP1a TP1a TP1 | - 0.4 to 3.3                            | 802.3ck 120G  | à.3.4.3    | V        |  |

|-------------------------------------------------------------------------------------------------------------|---------------|-----------------------------------------|---------------|------------|----------|--|

| tolerance Upper limit Lower limit                                                                           |               |                                         | 2.85<br>-0.35 |            | V<br>V   |  |

|                                                                                                             | Red           | eiver (each L                           | _ane)         |            |          |  |

| Signaling Rate, each lane                                                                                   | TP4           | 53.                                     | 125 ± 100 pp  | om         | GBd      |  |

| Peak-to-peak AC<br>common- mode voltage<br>Low-frequency, VCM <sub>LF</sub><br>Full-band, VCM <sub>FB</sub> | TP4           |                                         |               | 32<br>80   | mV       |  |

| Differential peak-to-<br>peak output voltage<br>Short mode<br>Long mode                                     | TP4           |                                         |               | 600<br>845 | mV<br>mV |  |

| Eye height                                                                                                  | TP4           | 15                                      |               |            | mV       |  |

| Vertical eye closure, VEC                                                                                   | TP4           |                                         |               | 12         | dB       |  |

| Common-mode to differential-mode return loss, RLdc                                                          | TP4           | IEEE802.3<br>ck<br>Equation<br>(120G-1) |               |            | dB       |  |

| Effective return loss, ERL                                                                                  | TP4           | 8.5                                     |               |            | dB       |  |

| Differential termination mismatch                                                                           | TP4           |                                         |               | 10         | %        |  |

| Transition time                                                                                             | TP4           | 8.5                                     |               |            | ps       |  |

| DC common-mode voltage tolerance Upper limit Lower limit                                                    | TP4           |                                         | 2.85<br>-0.35 |            | V        |  |

## **Optical Characteristics**

| Parameter                   | Symbol | Min      | Typical | Max    | Units | Notes |  |  |  |

|-----------------------------|--------|----------|---------|--------|-------|-------|--|--|--|

| Transmitter                 |        |          |         |        |       |       |  |  |  |

| Signaling rate, each lane   |        | 53.125 ± | GBd     |        |       |       |  |  |  |

| Modulation format           |        | PA       |         |        |       |       |  |  |  |

| Wavelength                  | λ      | 1304.5   |         | 1317.5 | nm    |       |  |  |  |

| Side-mode suppression ratio | SMSR   | 30       |         |        | dB    |       |  |  |  |

## pro-optics

| Average launch power, each lane                                       | P <sub>AVG</sub> | -2.9               |            | 4         | dBm   | 1 |  |  |

|-----------------------------------------------------------------------|------------------|--------------------|------------|-----------|-------|---|--|--|

| Outer optical modulation amplitude (OMA <sub>outer</sub> ), each lane | Рома             | -0.8               |            | 4.2       | dBm   | 2 |  |  |

| Transmitter and dispersion eye closure for PAM4 (TDECQ), each lane    | TDECQ            |                    |            | 3.4       | dB    |   |  |  |

| Launch power in OMA <sub>outer</sub> minus TDECQ, each lane           |                  | -2.2               |            |           | dB    |   |  |  |

| Average launch power of OFF transmitter, each lane                    | P <sub>off</sub> |                    |            | -15       | dBm   |   |  |  |

| Extinction ratio, each lane                                           | ER               | 3.5                |            |           | dB    |   |  |  |

| RIN <sub>21.4</sub> OMA                                               | RIN              |                    |            | -136      | dB/Hz |   |  |  |

| Optical return loss tolerance                                         | TOL              |                    |            | 21.4      | dB    |   |  |  |

| Transmitter reflectance                                               |                  |                    |            | -26       | dB    | 3 |  |  |

|                                                                       |                  | Receiver           |            |           |       |   |  |  |

| Signaling rate, each lane                                             |                  | 53.125 ±           | 100 ppn    | n         | GBd   |   |  |  |

| Modulation format                                                     |                  | PA                 | M4         |           |       |   |  |  |

| Center wavelength                                                     | λ                | 1304.5             |            | 1317.5    | nm    |   |  |  |

| Damage Threshold, each lane                                           | TH₀              | 5                  |            |           | dBm   | 4 |  |  |

| Average receive power, each lane                                      |                  | -5.9               |            | 4         | dBm   | 5 |  |  |

| Receive power (OMA <sub>outer</sub> ), each lane                      |                  |                    |            | 4.2       | dBm   |   |  |  |

| Receiver reflectance                                                  |                  |                    |            | -26       | dB    |   |  |  |

| Receiver sensitivity (OMA <sub>outer</sub> ), each lane               | SEN              |                    |            | -4.4      | dBm   | 6 |  |  |

| Stressed receiver sensitivity (OMA <sub>outer</sub> ), each lane      | SRS              |                    |            | -1.9      | dBm   | 7 |  |  |

| Conditions of Stress Receiver Sensitivity Test (Note 8)               |                  |                    |            |           |       |   |  |  |

| Condit                                                                | ions of St       | tress Receiver Sen | sitivity T | est (Note | 8)    |   |  |  |

| Stressed eye closure<br>for PAM4 (SECQ),<br>lane under test | 3.4 |   | dB  |  |

|-------------------------------------------------------------|-----|---|-----|--|

| OMA <sub>outer</sub> of each aggressor lane                 | 4.2 | C | dBm |  |

#### Notes:

- 1. Average launch power, each lane (min) is informative and not the principal indicator of signal strength. A transmitter with launch power below this value cannot be compliant; however, a value above this does not ensure compliance.

- 2. Even if the TDECQ < 1.4 dB, the OMAouter (min) must exceed these values.

- 3. Transmitter reflectance is defined looking into the transmitter.

- 4. The receiver shall be able to tolerate, without damage, continuous exposure to an optical input signal having this average power level. The receiver does not have to operate correctly at this input power.

- 5. Average receive power, each lane (min) is informative and not the principal indicator of signal strength. A received power below this value cannot be compliant; however, a value above this does not ensure compliance.

- 6. Receiver sensitivity (OMA<sub>outer</sub>), each lane (max) is informative and is defined for a transmitter with SECQ of 0.9 dB.

- 7. Measured with conformance test signal for BER = $2.4x10^{-4}$ .

- 8. These test conditions are for measuring stressed receiver sensitivity. They are not characteristics of the receiver.

#### **Digital Diagnostic Specifications**

The following digital diagnostic characteristics are defined over the normal operating conditions unless otherwise specified.

| Parameter                               | Symbol       | Min  | Max | Units | Notes                            |

|-----------------------------------------|--------------|------|-----|-------|----------------------------------|

| Temperature monitor absolute error      | DMI_Temp     | -3   | 3   | degC  | Over operating temperature range |

| Supply voltage monitor absolute error   | DMI_VCC      | -0.1 | 0.1 | V     | Over full<br>operating<br>range  |

| Channel RX power monitor absolute error | DMI_RX_Ch    | -2   | 2   | dB    | 1                                |

| Channel Bias current monitor            | DMI_Ibias_Ch | -10% | 10% | mA    |                                  |

| Channel TX power monitor absolute error | DMI_TX_Ch    | -2   | 2   | dB    | 1                                |

Notes:

1. Due to measurement accuracy of different single mode fibers, there could be an additional +/-1 dB fluctuation, or a +/- 3 dB total accuracy

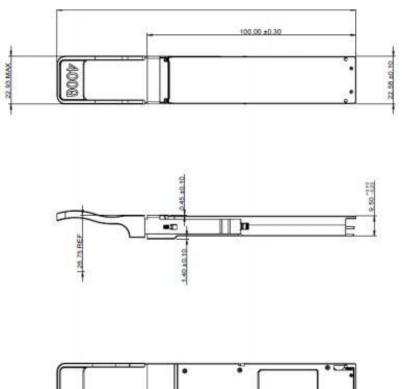

### **Mechanical Drawing**

Figure 6. Mechanical Outline

#### **ESD**

This transceiver is specified as ESD threshold 1kV for high speed data pins and 2kV for all other electrical input pins, tested per MIL-STD-883, Method 3015.4 /JESD22-A114-A (HBM). However, normal ESD precautions are still required during the handling of this module. This transceiver is shipped in ESD protective packaging. It should be removed from the packaging and handled only in an ESD protected environment.

#### Laser safety

This is a Class I Laser Product, or Class 1 Laser Product according to IEC/EN 60825-1:2014.

This product complies with 21 CFR 1040.10 and 1040.11 except for conformance with IEC 60825-1 Ed. 3., as described in Laser Notice No. 56, dated May 8, 2019.

Caution: Use of controls or adjustments or performance of procedures other than those specified herein may result in hazardous radiation exposure.